Fabless Company Financial Model

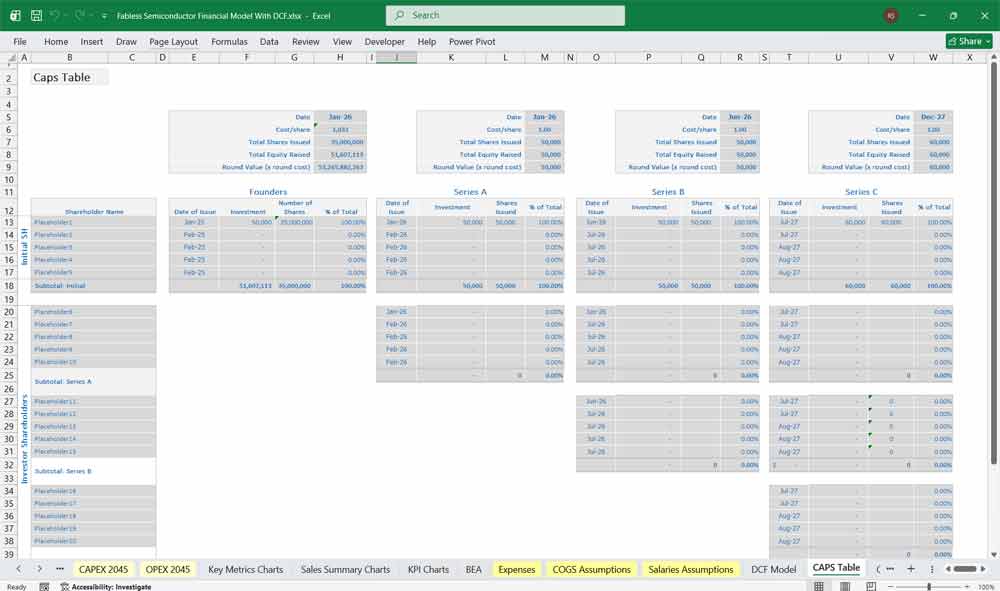

This 20-Year, 3-Statement Excel Fabless Company Financial Model includes up to 5 revenue streams from developing chip architecture, intellectual property (IP), and final design. Cost structures, Discounted Cash Flow (DCF) with Terminal Value, Sensitivity Analysis, and WACC and financial statements to forecast the financial health of your Fabless Semiconductor company.

20-Year Financial Model for a Fabless Semiconductor Company

This very extensive 20 Year Fabless Semi Model involves detailed revenue projections, cost structures, capital expenditures, OPEX, and other financing requirements. This model provides a thorough understanding of the financial viability, profitability, and cash flow position of your fabless company. Includes: 20x Income Statements, Cash Flow Statements, Balance Sheets, CAPEX sheets, OPEX Sheets, Statement Summary Sheets, and Revenue Forecasting Charts with the revenue streams, BEA charts, sales summary charts, employee salary tabs and expenses sheets. Semiconductor Fab Financial Model

Model Architecture Overview

A complete fabless semiconductor financial model typically includes:

Revenue build by product line, end market, and pricing

Cost structure driven by foundry wafers, packaging/test, and royalties

Operating expenses heavily weighted toward R&D

Working capital modeling (inventory, AR, AP)

Cash flow reflecting capex and volatile operating cash flow

Balance sheet with strong cash positions and limited fixed assets

The model is monthly for startups and mature public companies.

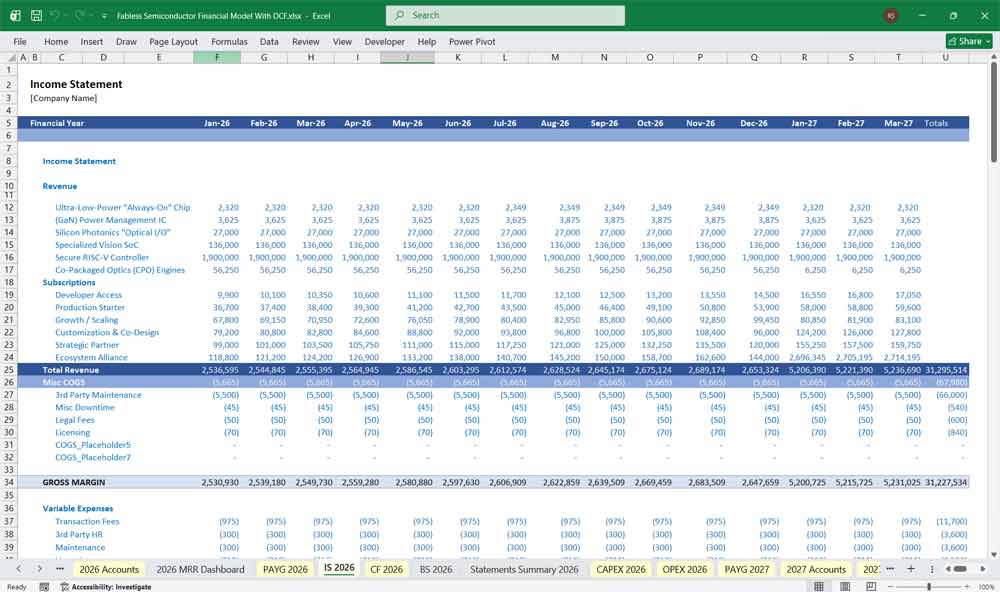

Income Statement

The Income Statement reflects the company’s profitability over a period, driven by a “fabless” cost structure where Cost of Revenue (CoR) is primarily variable payments to third-party suppliers.

A. Revenue Examples

Product Revenue: Sales of designed semiconductor chips (ICs). Often broken down by product family (e.g., microcontrollers, connectivity, sensors) or end market (Auto, IoT, Consumer).

Licensing & Royalty Revenue: Fees for granting IP (Intellectual Property) blocks (e.g., ARM cores, interconnect, interface IP) to other companies. Royalties are typically a percentage of the licensee’s chip selling price.

NRE (Non-Recurring Engineering) Revenue: One-time fees charged to customers for custom design work. This is recognized as revenue upon completion of milestones or delivery, not as a lump sum.

B. Cost of Revenue (CoR)

Wafer Costs: Payments to foundries (e.g., TSMC, GlobalFoundries) for fabricating the silicon wafers. This is the largest component of CoR. Modeled as a cost per wafer or cost per unit.

Assembly, Test, and Packaging (ATP) Costs: Payments to outsourced assembly and test (OSAT) providers.

Royalty Costs: Payments to IP licensors (e.g., ARM) for cores used in the company’s own products. This is a pass-through cost, incurred only when product revenue using that IP is recognized.

Inventory Write-downs/Excess & Obsolescence: Critical for semiconductors due to rapid technological change and demand volatility.

Logistics & Tariffs: Shipping and import duties.

C. Gross Profit & Gross Margin

Gross Profit = Total Revenue – Total CoR.

Gross Margin % = Gross Profit / Revenue. A key metric indicating design efficiency and pricing power. Fabless model typically yields 45-65%+ gross margins.

D. Operating Expenses (OpEx)

Research & Development (R&D):

Engineering Salaries & Benefits: The largest R&D cost for a design house.

Tape-Out Costs: Multi-million dollar, non-recurring payments to the foundry for mask sets and initial production runs for a new chip design. These are expensed as incurred (not capitalized), making R&D lumpy.

EDA Tools & IP Licenses: Software for chip design (Synopsys, Cadence) and licenses for third-party IP.

Prototype & Validation Costs.

Sales, General & Administrative (SG&A):

Sales & Marketing Salaries, Commissions.

General Management, Finance, Legal.

Facilities, IT, Professional Fees.

E. Other Income/(Expense)

Interest Income/(Expense): From cash balances and debt.

Foreign Exchange Gain/(Loss): Due to global operations and multi-currency transactions.

F. Taxes

Income Tax Provision: Often includes complexities of R&D tax credits and geographic profit shifting.

G. Net Income

The bottom-line profit after all expenses and taxes.

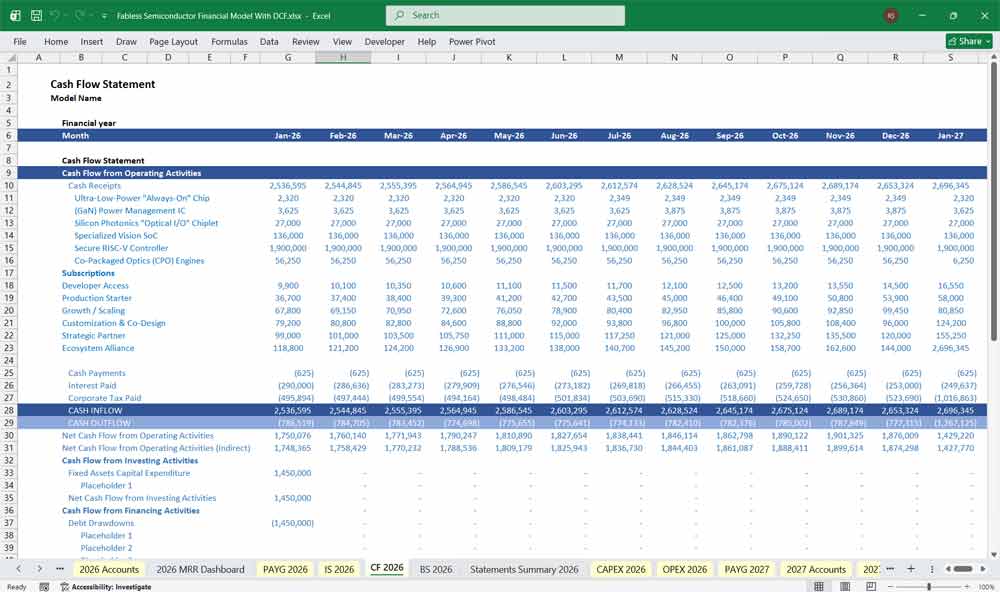

Fabless Company Cash Flow Statement

The Cash Flow Statement is critical due to heavy upfront cash outflows for R&D and inventory builds before revenue is realized.

A. Cash Flows from Operating Activities (CFO)

Starting Point: Net Income.

Add-back Non-Cash Items:

Depreciation & Amortization (of office equipment, software).

Stock-Based Compensation.

Inventory Write-downs (added back as it was a non-cash charge on the Income Statement).

Changes in Working Capital (Crucial for Fabless):

Accounts Receivable (A/R): Cash use when A/R increases (sales on credit).

Inventory: Major cash use. Inventory is built from wafers through ATP to finished goods, often taking 90-180 days. An increase in inventory consumes cash.

Prepaid Expenses & Other Assets.

Accounts Payable (A/P): Source of cash. Primarily payments due to foundries and OSATs. An increase in A/P conserves cash.

Accrued Liabilities (salaries, taxes, bonuses).

Net Cash from Operations: Indicates if core business generates cash after funding working capital needs.

B. Cash Flows from Investing Activities (CFI)

Capital Expenditures (CapEx): Unlike an IDM (Integrated Device Manufacturer), CapEx is low. Mainly consists of computers, lab equipment, and office build-outs.

Purchases of Short-term Investments (if parking excess cash).

Acquisition of Intellectual Property or a Business (if applicable).

C. Cash Flows from Financing Activities (CFF)

Proceeds from Issuance of Equity/Stock (e.g., venture capital, IPO, follow-on offering).

Repurchase of Stock / Treasury Stock.

Proceeds from/(Repayment of) Debt.

Payment of Dividends (rare for growth-stage fabless companies).

D. Net Change in Cash

Sum of CFO, CFI, and CFF. Added to opening cash balance to get closing cash.

Fabless Company Balance Sheet

The Balance Sheet provides a snapshot of the company’s financial position, characterized by low PP&E and significant intangible value in its IP and design talent.

ASSETS

Current Assets:

Cash & Cash Equivalents: The lifeblood for funding R&D cycles.

Short-Term Investments: Marketable securities.

Accounts Receivable: Net of an allowance for doubtful accounts.

Inventory (in three stages):

Wafer Inventory (Work-in-Process at foundry).

Die Bank / Finished Wafers.

Finished Goods (after ATP).

Prepaid Expenses & Other Current Assets.

Non-Current Assets:

Property, Plant & Equipment (PP&E), Net: Office equipment, computers, lab gear. Net of accumulated depreciation. Relatively small compared to an IDM.

Intangible Assets: Purchased IP, patents (if acquired).

Goodwill: From acquisitions.

Other Long-Term Assets.

LIABILITIES & STOCKHOLDERS’ EQUITY

Current Liabilities:

Accounts Payable: Primarily to foundries and OSATs. A key financing source.

Accrued Compensation & Benefits.

Accrued Liabilities (tape-out costs, taxes).

Deferred Revenue: For unfulfilled obligations (e.g., undelivered NRE milestones).

Current Portion of Long-Term Debt.

Long-Term Liabilities:

Long-Term Debt, Net of Current Portion.

Other Long-Term Liabilities (leases, etc.).

Stockholders’ Equity:

Common Stock.

Additional Paid-In Capital (APIC): Funds from equity issuance.

Retained Earnings (Accumulated Deficit): Cumulative net income/loss over company life. Often negative for many years during high-growth R&D phase.

Accumulated Other Comprehensive Income (Loss).

Treasury Stock (if shares repurchased).

Key Modeling Drivers & Metrics Specific To Fabless

Unit Economics: Average Selling Price (ASP) and Cost per Unit (or Cost per Wafer). ASP often erodes over time; cost per unit declines with yield learning and process maturity.

Foundry/OSAT Agreements: Minimum purchase commitments, wafer pricing (dependent on volume and process node), and payment terms drive CoR and A/P.

Inventory Modeling: Must model the fab cycle time and ATP lead time to correctly forecast inventory build and cash conversion cycle.

Tape-Out Schedule & R&D Amortization: The company’s future tape-outs (new product introductions) create large, discrete R&D expenses. R&D as % of Revenue is a key benchmark.

Key Financial Metrics:

Gross Margin % (and by product line).

Operating Margin % (EBIT Margin).

Free Cash Flow = CFO – CapEx. Ultimate measure of self-sustainability.

Cash Conversion Cycle = DSO + DIO – DPO. Target is to minimize it.

Book-to-Bill Ratio: For gauging demand vs. shipment trends.

This model structure provides a comprehensive framework to analyze the past performance and future potential of a fabless semiconductor company, capturing its unique operational and financial DNA.

Example Fabless CAPEX in The Model

Perpetual EDA Software Licenses

Third-Party IP Licenses

- Photolithographic Mask Sets (COT Model)

- High-Performance Compute (HPC) Clusters

- Hardware Emulators

- FPGA Prototyping Racks

- Automated Test Equipment (ATE)

Example Fabless OPEX in The Model

EDA Software Subscriptions

Base Software Subscription Fees

MPW (Multi-Project Wafer) Shuttle Fees

Base Fabrication/Area Fees

Prototype Assembly & Test Feess

Packaging Materials (QFN, BGA)

- Assembly Labor & Process

Field Application Engineers (FAEs) Fees

Travel and Living Expenses

Reference Design Development

EDA Software and IP Licensing

6-tier subscription model add-on for your fabless semiconductor company

This model structures customers by scale, technical depth, and strategic partnership level. The entry tiers focus on developer access, evaluation silicon, and basic support, enabling startups and smaller OEMs to prototype and launch products. Mid-level tiers introduce guaranteed wafer allocation, dedicated technical account management, performance optimization, and roadmap visibility to support scaling production. Upper tiers transition into co-design, semi-custom silicon modifications, long-term supply agreements, and reserved foundry capacity. At the highest level, customers gain full custom ASIC collaboration, ecosystem integration, executive alignment, and multi-year strategic partnerships—shifting the relationship from transactional chip supplier to long-term silicon platform partner.

Tier 1 – Developer Access (Entry / Evaluation Tier)

Target: Startups, university labs, early-stage product teams

What They Get:

Limited-volume chip supply (engineering samples)

Access to SDK, drivers, and documentation

Basic reference designs

Community forum access

Standard email support (48–72 hour SLA)

Simulation models (FPGA emulation or virtual silicon)

Purpose:

Encourage ecosystem adoption and lower barrier to entry. This tier focuses on developer onboarding and early product experimentation.

Revenue Model:

Low monthly subscription

Pay-per-chip pricing

Add-on for evaluation boards

Tier 2 – Production Starter Tier

Target: Small to mid-sized OEMs moving to low-volume production

What They Get:

Guaranteed wafer allocation (low volume)

Production-grade silicon

Priority firmware updates

Design review session (quarterly)

Access to certified manufacturing partners

Basic lifecycle roadmap visibility

Added Value:

Reduces risk of supply disruption and shortens time to production readiness.

Revenue Model:

Higher subscription + committed minimum order volume

Optional firmware maintenance subscription

Tier 3 – Growth / Scaling Tier

Target: High-growth OEMs and system integrators

What They Get:

Reserved wafer capacity (mid-volume)

Dedicated technical account manager (TAM)

Advanced performance optimization support

Custom firmware configuration options

Early access to next-gen silicon roadmap

Integration support with foundry and OS ecosystem

Strategic Benefit:

Enables scaling customers to optimize performance, power, and cost at system level.

Revenue Model:

Annual contract

Wafer allocation commitment

Customization fees

Tier 4 – Customization & Co-Design Tier

Target: Enterprise OEMs, automotive, AI infrastructure providers

What They Get:

Semi-custom silicon modification (IP block adjustments)

Co-design engineering collaboration

Priority tape-out scheduling

Long-term supply agreement (5–7 years)

Extended lifecycle support (automotive/industrial grade)

Dedicated FAEs (Field Application Engineers)

Strategic Benefit:

Deep integration into customer product architecture, increasing switching costs.

Revenue Model:

High annual subscription

NRE (Non-Recurring Engineering) fees

Long-term wafer purchase agreements

Tier 5 – Strategic Partner Tier

Target: Large hyperscalers, telecom giants, automotive Tier 1 suppliers

What They Get:

Custom ASIC development pathway

Joint IP ownership models

Silicon roadmap influence

Reserved foundry capacity (TSMC/Samsung node priority)

Dedicated support team (24/7 SLA)

Supply chain risk management support

Competitive Edge:

Transforms relationship from supplier → strategic silicon partner.

Revenue Model:

Multi-year strategic contract

Capacity reservation fees

IP licensing revenue share

Tier 6 – Ecosystem Alliance / Platform Tier

Target: Platform builders, cloud AI companies, national infrastructure players

What They Get:

Full platform-level integration (silicon + software + ecosystem)

Private roadmap collaboration sessions

Custom silicon + packaging (chiplet integration, advanced nodes)

Co-marketing & joint go-to-market support

Early access to emerging node technologies

Dedicated executive steering committee

Strategic Role:

This tier positions the fabless company as a platform architect, not just a chip designer — similar to how Apple Inc. vertically integrates silicon strategy into ecosystem design.

Revenue Model:

Large multi-year platform agreements

Revenue sharing models

Joint venture or equity participation options

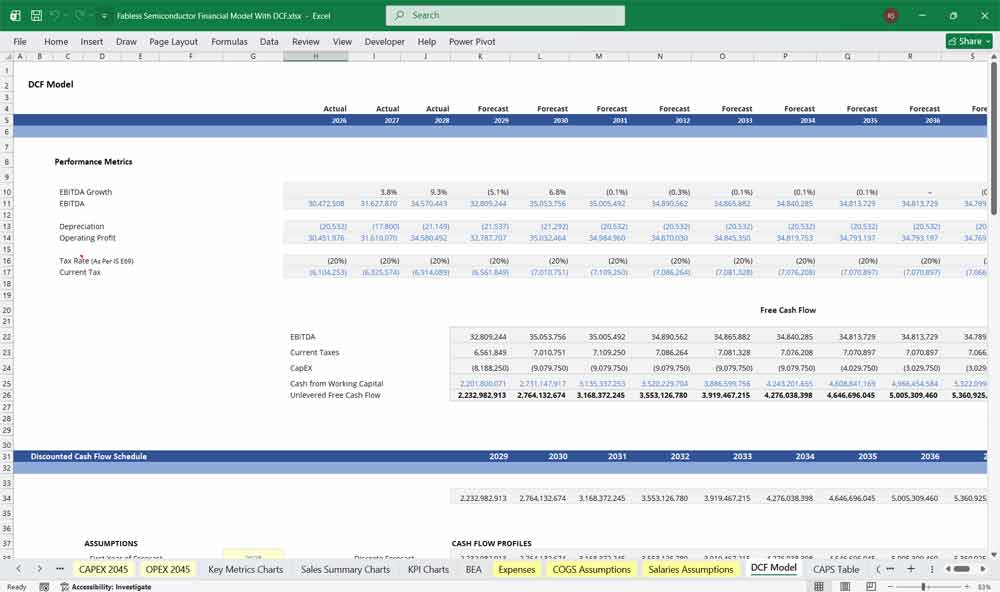

Valuing Your Chip Design House With A DCF

Discounted Cash Flow (DCF) for a Fabless Company

For your Fabless Company a Discounted Cash Flow (DCF) analysis is less about valuing “dirt and diesel” and more about valuing “silicon and software.” Revenue forecasts are driven by product innovation, design wins, market share growth, average selling prices, and end-market demand, while costs include research and development, tape-out expenses, third-party foundry manufacturing, and sales and marketing. The projected free cash flows over a defined high-growth period, along with a terminal value reflecting long-term scalability and intellectual property strength, are discounted to present value to determine the company’s intrinsic value.

WACC for a Fabless Company

Weighted Average Cost of Capital (WACC) is used as the discount rate in valuing a fabless company and reflects the blended cost of equity and debt financing. Fabless firms typically have lower capital expenditure requirements than integrated manufacturers but face significant technology risk, product cycle volatility, customer concentration, and competitive pressures. The WACC captures investors’ required returns, the company’s capital structure, and any tax benefits of debt, representing the minimum return necessary to justify investment in the business.

Sensitivity Analysis for a Fabless Semiconductor Company

Sensitivity analysis is especially important in valuing a fabless company due to uncertainties in product adoption rates, pricing, gross margins, design cycle success, and reliance on external foundries. Analysts commonly test changes in key assumptions such as revenue growth, operating margins, R&D intensity, working capital needs, and WACC. By evaluating how variations in these inputs affect the DCF valuation, sensitivity analysis highlights the most influential value drivers and provides a range of potential outcomes to support strategic and investment decisions.

Final Notes on the Financial Model

This 20 Year Fabless Company Financial Model focuses on balancing capital expenditures with steady revenue growth from your product line. By optimizing operational costs, and power efficiency, and maximizing high-margin services, the models ensure sustainable profitability and cash flow stability.

Download Link On Next Page

Download Link On Next Page